На мероприятии IEDM 2024 тайваньский производитель микросхем TSMC поделился с общественностью новыми подробностями своей предстоящей технологической нормы 2-нм, основанной на новом типе транзисторов GAAFET с нанолистами.

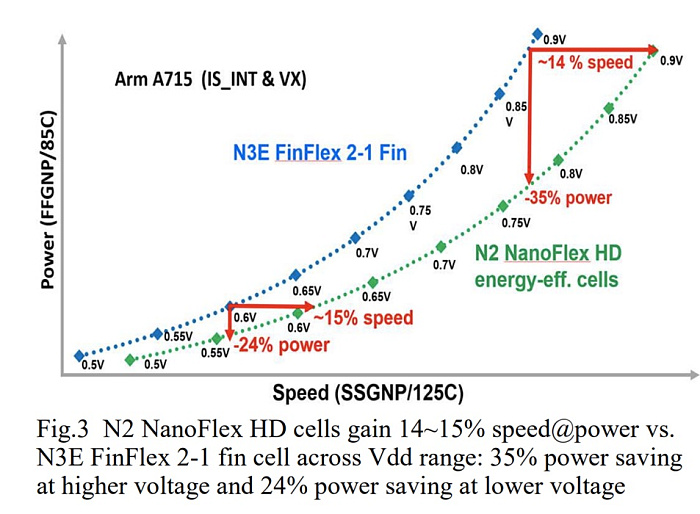

По сравнению с текущими 3 нанометрами, новый техпроцесс сможет предложить 15% повышение плотности размещения транзисторов, 15% рост производительности при неизменном потреблении или на 24-35% меньшее потребление при неизменной производительности, но тут все сильно зависит от требуемой тактовой частоты и используемого напряжения.

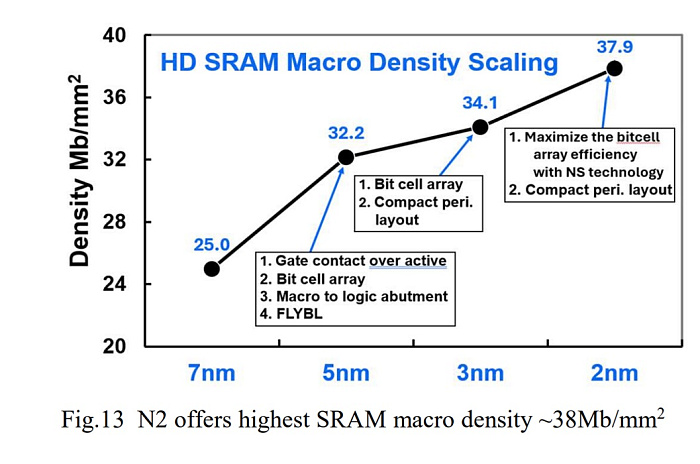

Другим плюсом предстоящего техпроцесса является уменьшение размера ячеек SRAM, изменение размера которых является большой проблемой у производителей полупроводников, благодаря чему получится разместить больше кэша в меньшей площади кристалла.

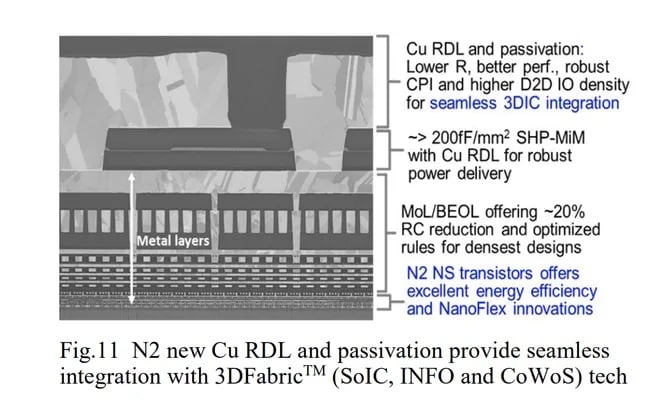

Что касается других изменений, инженеры TSMC разработали новые MoL, BEOL и far-BEOL, снизив общее сопротивление на 20% и, тем самым, повысив эффективность транзисторов.