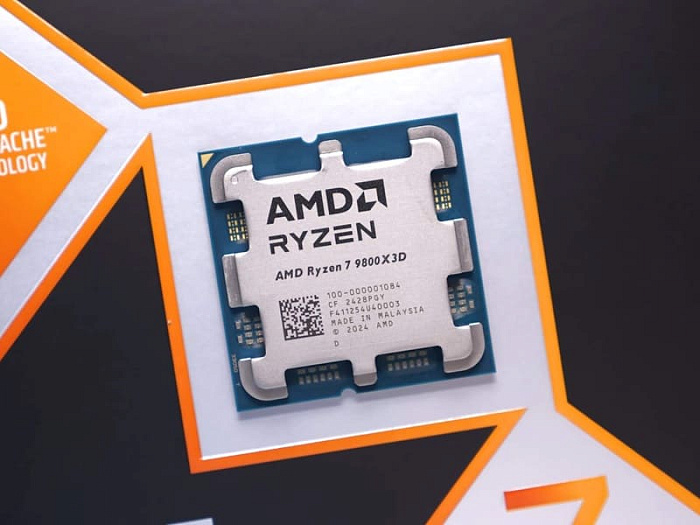

Технология наложения дополнительного кэша 3D V-Cache помогла AMD завоевать лидерство в области игровой производительности центральных процессоров. На данный момент у технологии есть ограничение в виде использования только для кэша третьего уровня, при этом компания вовсю занимается его решением.

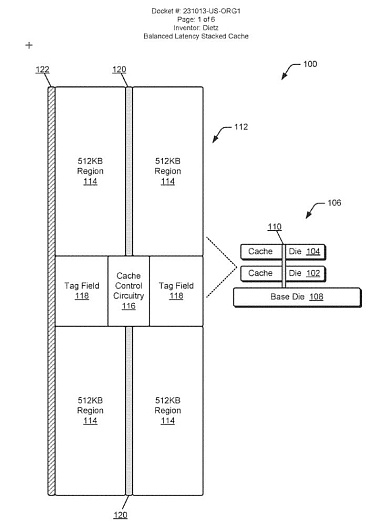

Работяги компании опубликовали исследовательскую работу US20260003794A1 под наименованием «Накопленный кэш со сбалансированной задержкой». В ней рассказывается, как можно применить 3D V-Cache к кэшу процессора второго уровня и, судя по всему, разработка происходит вполне успешно.

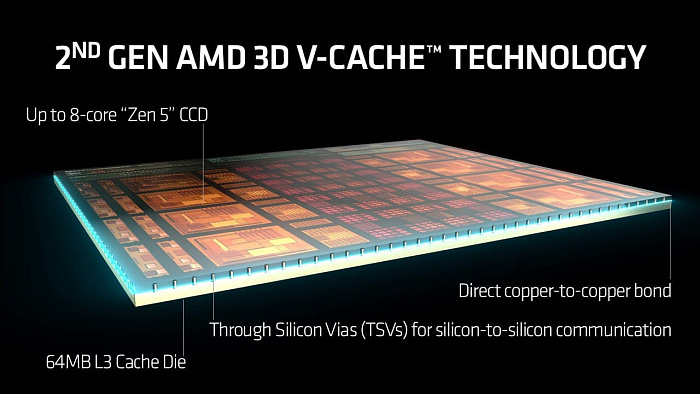

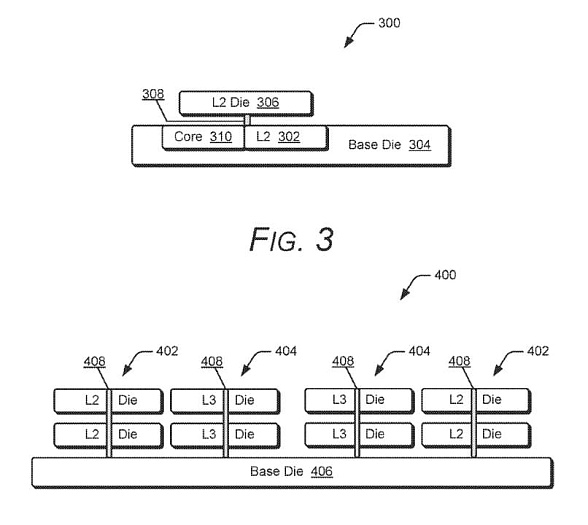

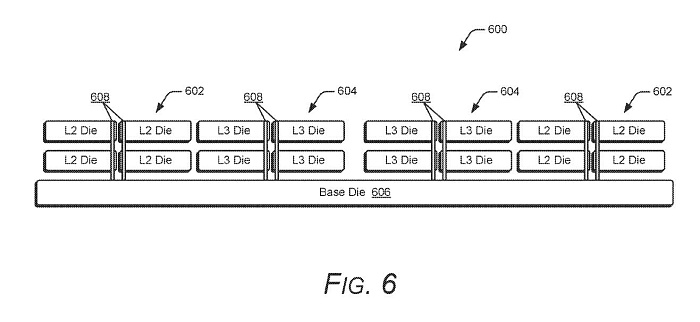

Согласно содержанию, компания хочет накладывать на плитку логики сразу две плитки памяти: одну для кэша L3, вторую — для кэша L2. Если первая предлагает 64 Мбайта дополнительной памяти, то вторая — всего 4 Мбайта, набранных четырьмя блоками по 512 Кбайт, но, судя по изображениям, можно наложить два слоя на каждый CCD, что даёт 8 Мбайт. К слову, сейчас ядра на Zen 5 предлагают до 8 Мбайт кэша второго уровня на вычислительный чиплет, но каждое ядро имеет доступ только к 1 Мбайту.

Интересен момент производительности, ведь наложение кэша снижает задержку обращения с 14 до 12 циклов, или примерно на 15% по сравнению со встроенным в кристалл планарным кэшем, отбирающим транзисторный бюджет и занимающим много места. Снижение задержки, понятное дело, положительно сказывается на итоговой производительности, особенно в случае кэш-промаха, а также улучшает энергоэффективность процессора в целом.

«В аспектах описанных методик конфигурация системы многоуровневого кэша уменьшает задержку ответа при доступе к многоуровневому кэшу, а также обеспечивает функцию энергосбережения. Система многоуровневого кэша повышает производительность передачи данных и имеет меньшую задержку, чем обычный планарный кэш, построенный на одном кристалле. Примечательно, что соединительные каналы направляются в центр системы многоуровневого кэша и из него. Это позволяет избежать добавления промежуточных этапов (также называемых здесь этапами канала), как в обычном планарном кэше, для маршрутизации данных по одной части кэша для достижения части кэша, которая находится дальше от системы ввода-вывода данных.

В описанных технологиях соединительные переходы, которые маршрутизируются по центру системы наложенного кэша, создают сбалансированные (или идентичные) задержки между двумя половинами системы наложенного кэша на кристалле (например, первого кристалла кэша и, по меньшей мере, второго кристалла кэша). Например, обычный планарный кэш L2M объёмом 1 Мбайт имеет задержку в 14 циклов, в то время как наложенный кэш L2M объёмом 1 Мбайт, реализованный с использованием описанных методов, имеет задержку всего в 12 циклов. Это обеспечивает реализацию более масштабируемого кэша, чем обычный планарный кэш, при этом достигается такая же или лучшая задержка цикла.

Соответственно, описанные аспекты многоуровневого кэша со сбалансированной задержкой обеспечивают меньшую задержку для запроса доступа, и данные возвращаются из кэша данных быстрее. Существует также экономия электроэнергии за счёт того, что запрос доступа выполняется за меньшее количество циклов, поэтому, например, кэш L2 не включается так долго, а также экономия электроэнергии при более быстром переходе кэша из активного состояния в состояние ожидания. Кроме того, длина проводов в матрице кэш-памяти короче, что эффективно приводит к уменьшению ёмкости, а также к экономии электроэнергии. Кроме того, нагрузка на сигнал меньше, поскольку сигналы проходят только половину расстояния для запроса доступа и возврата данных. Кроме того, выделяется меньше тепла в результате экономии электроэнергии, меньшей ёмкости и передачи сигналов на меньшее расстояние».